| Advanced V                                                                                        | LSI Design            |                                                             |

|---------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------|

| JK Flip-Flop Model                                                                                | qn q                  |                                                             |

| entity JKFF is<br>port (SN, RN, J, K, CLK; in bit                                                 | KN                    | -574                                                        |

| Q: inout bit; QN: out bit<br>end JKFF;                                                            |                       | 1                                                           |

| architecture JKFF1 of JKFF is<br>begin                                                            |                       |                                                             |

| process (SN, RN, CLK)<br>begin                                                                    | see Note 2            |                                                             |

| if RN = '0' then Q<= '0' after<br>elsif SN = '0' then Q<= '1' a<br>elsif CLK = 0' and CLK event f | fter 10 ms;           | RN=0 will dear the PP<br>SN=0 will set the PP<br>see Note 3 |

| Q <= (J and not Q) or (not<br>end if;<br>end process;                                             | K and Q) after 10 ns; | see Note 4                                                  |

| QN <= not Q;<br>end 30°F1;                                                                        | seu Note 5            |                                                             |

|                                                                                                   | © A. Milenkovic       | 13                                                          |

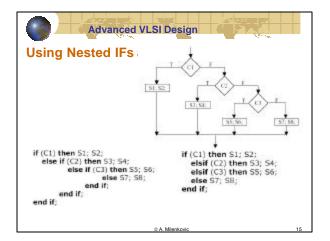

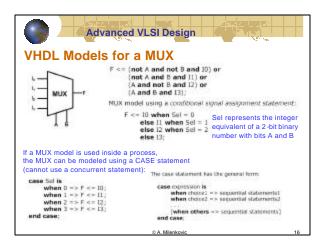

| Advanced VLS                                                                                                                   | IDesign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

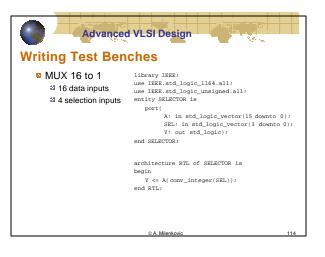

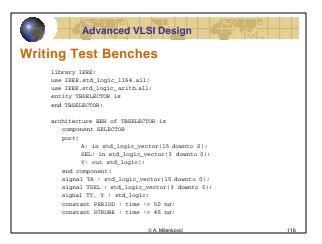

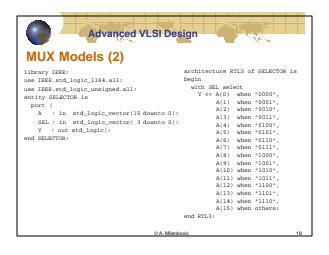

| <pre>MUX Models (1)  library IEEF; use IEEE.std_logic_li64.al; use IEEE.std_logic_unsigned.al; entity SELECTOR is port (</pre> | architecture RTL1 of SELECTOR is begin<br>p0 : process (A, SEL)<br>begin<br>if (SEL = '00007' then Y <= A(0);<br>elsif (SEL = '0001') then Y <= A(1);<br>elsif (SEL = '0011') then Y <= A(2);<br>elsif (SEL = '0011') then Y <= A(2);<br>elsif (SEL = '0011') then Y <= A(3);<br>elsif (SEL = '0010') then Y <= A(4);<br>elsif (SEL = '0101') then Y <= A(5);<br>elsif (SEL = '0101') then Y <= A(6);<br>elsif (SEL = '0101') then Y <= A(7);<br>elsif (SEL = '0101') then Y <= A(1);<br>elsif (SEL = '0101') then Y <= A(1);<br>elsif (SEL = '1001') then Y <= A(1);<br>elsif (SEL = '1101') then Y <= A(11);<br>elsif (SEL = '1101') then Y <= A(12);<br>elsif (SEL = '110') then Y <= A(12);<br>elsif (SEL |

| ۵                                                                                                                              | A. Milenkovic 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

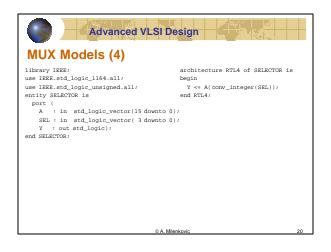

| Advanced VLSI                                                                                                                    | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MUX Models (3)                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre>library IEEE;<br/>use IEEE.std_logic_1164.all;<br/>use IEEE.std_logic_unsigned.all;<br/>entity SELECTOR is<br/>port (</pre> | architecture RTL2 of SELECTOR is<br>begin<br>pl: process (A, SEL)<br>begin<br>case SEL is<br>when "0000" $\Rightarrow Y (= A(0));$<br>when "0010" $\Rightarrow Y (= A(0));$<br>when "0010" $\Rightarrow Y (= A(2));$<br>when "0010" $\Rightarrow Y (= A(2));$<br>when "0101" $\Rightarrow Y (= A(2));$<br>when "0100" $\Rightarrow Y (= A(3));$<br>when "0100" $\Rightarrow Y (= A(4));$<br>when "0100" $\Rightarrow Y (= A(5));$<br>when "0101" $\Rightarrow Y (= A(5));$<br>when "0101" $\Rightarrow Y (= A(5));$<br>when "0101" $\Rightarrow Y (= A(5));$<br>when "101" $\Rightarrow Y (= A(10);$<br>when "101" $\Rightarrow Y (= A(10);$<br>when "100" $\Rightarrow Y (= A(11);$<br>when "110" $\Rightarrow Y (= A(11);$<br>when "110" $\Rightarrow Y (= A(14);$<br>when "110" $\Rightarrow Y (= A(14);$<br>when uthers $\Rightarrow Y (= A(15);$<br>end reas:<br>end process; |

| ©A                                                                                                                               | Milenkovic 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

A. Milenkovic

|                                                                                                                |                                                                                | Actual Pa                                              | rameter                                   |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|

| Mode                                                                                                           | Class                                                                          | Procedure Call                                         | Function Cal                              |

| in <sup>1</sup><br>out/inout                                                                                   | constant <sup>2</sup><br>signal<br>variable<br>signal<br>variable <sup>3</sup> | expression<br>signal<br>variable<br>signal<br>variable | expression<br>signal<br>n/a<br>n/a<br>n/a |

| and a second |                                                                                | variable                                               |                                           |

Files and Text IO

© A. Milenkovic

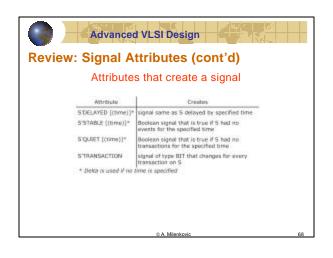

| Ŭ     | nal Attribu<br>Attribu | ites associated with signals                                           |  |

|-------|------------------------|------------------------------------------------------------------------|--|

|       | Attribute              | that return a value                                                    |  |

|       | SIEVENT                | True if an event occurred during the current<br>defta, etce false      |  |

|       | SWCTIVE                | True If a transaction occurred during the<br>current delta, else faise |  |

|       | SLAST_EVENT            | Time elapsed since the previous event on 5                             |  |

|       | S'LAST_VALUE           | Value of 5 before the previous event on 5                              |  |

|       | SLAST_ACTIVE           | Time elapsed since previous transaction on S                           |  |

| A'eve | ent - true if a char   | nge in S has just occurred                                             |  |

|       |                        | just been reevaluated, even if A does not change                       |  |

| Arra | y Attribut                                      |                                      |                                                                         |  |

|------|-------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------|--|

|      | Type ROM is arres (0 to 1<br>Signal ROM1 : ROM; | 5, 7 downto (1) of 5                 | t;                                                                      |  |

|      | Attributal                                      | Returns                              | Examples                                                                |  |

|      | ALEPTON:                                        | KHS beand of Mit<br>index range      | ROMILEPT(1) = 8<br>ROMILEFT(2) = 7                                      |  |

|      | ANDGHTON                                        | right bound of Nth<br>Index range    | RDPH1R0GHT(1) = 15<br>R0PH1R0GHT(2) = 0                                 |  |

|      | WHEEH(N)                                        | targest ticeed of<br>Nth Index targe | 80P114EH(1) = 15<br>80P(14EH(2) = 7                                     |  |

|      | WLOWINI                                         | smallest bound of<br>Nth index range | 8.0H11.0W11) = 0<br>8.0H11.0W12) = 0                                    |  |

|      | AYRANGE(N)                                      | N/h index tange:                     | RDH1WANGE(1) = 0 to 15<br>RDH1WANGE(2) = 7 dewyte 0                     |  |

|      | AVREVERSE_RANGE(N)                              | Rith Index tange<br>(conversion)     | ROHLREVERSE_RANGE(1) =<br>15 devente 0<br>ROHLREVERSE_RANGE(2) = 0 to 7 |  |

|      | ALENGTH(N)                                      | size of Nth Index<br>range           | RDH1'LENGTH(1) = 16<br>RDH1'LENGTH(2) = 8                               |  |

|      | e either an array na                            |                                      | 1000 00000 100150 1000                                                  |  |

|    |                   | ·0'             | - '1' | <u>'Z'</u>      | OR          | 'X'                | ·0'                | -117  | <u>'Z'</u> |

|----|-------------------|-----------------|-------|-----------------|-------------|--------------------|--------------------|-------|------------|

| X' | 'X'               | ·0'             | 'X'   | 'X'             | 'X'         | 'X'                | 'X'                | - 147 | 'X'        |

| 0' | <u>.0,</u>        | ·0'             | .0,   | ·0 <sup>,</sup> | <u>.0,</u>  | 'X'                | ·0'                | ·1'   | 'X'        |

| 4' | <u>'X'</u>        | ·0 <sup>7</sup> | 42    | 'X'             | 47          | ·1'                | 47                 | ·1'   | ·1'        |

| Z  | L. <sub>X</sub> . |                 |       |                 | J L <u></u> | -1. <sub>X</sub> . | -1. <sub>X</sub> . |       |            |

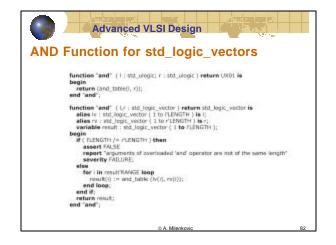

| Advanced VLSI                                                                                                                | Design                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| IEEE 1164 Standard L                                                                                                         | ogic                                                                                           |

| a '0' – Forcing 0<br>a '1' – Forcing 1                                                                                       | <sup>n</sup> If forcing and weak signal are<br>tied together, the forcing signal<br>dominates. |

| <ul> <li>a' 'Z' – High impedance</li> <li>a' 'W' – Weak unknown</li> <li>a' 'L' – Weak 0</li> <li>a' 'H' – Weak 1</li> </ul> | Useful in modeling the internal operation of certain types of ICs.                             |

| ≊ 'H – Weak 1<br>≊ '-' – Don't care                                                                                          | In this course we use a subset<br>of the IEEE values: X10Z                                     |

| 0                                                                                                                            | A. Milenkovic 79                                                                               |

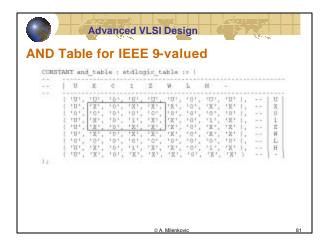

| COR | TN: | T 18       |                                         | lon_ta                | bla i                            |                                         | ogic_                                          | :pble                                 | 10.1                                     |   | <br>       |

|-----|-----|------------|-----------------------------------------|-----------------------|----------------------------------|-----------------------------------------|------------------------------------------------|---------------------------------------|------------------------------------------|---|------------|

|     | 1   |            | X                                       | 0                     | 1                                | <u>z</u> .                              | N                                              | F                                     | 34                                       | + | <br>       |

|     |     | dedendeden | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX | ж<br>х<br>о<br>о<br>х | 11<br>11<br>11<br>11<br>11<br>11 | NOT | U<br>N<br>N<br>N<br>N<br>N<br>N<br>N<br>N<br>N | N N N N N N N N N N N N N N N N N N N | U. U |   | ONOHNSHH - |

| 17. |     |            |                                         |                       |                                  |                                         |                                                |                                       |                                          |   |            |

A. Milenkov